Добавление testbench'ей на языке Verilog в проект Vivado

|

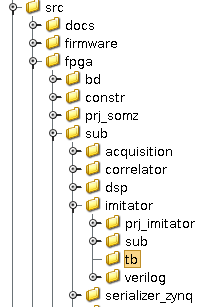

Пусть у нас есть дизайн для Vivado, проект которого разворачивается в соответствии со статьей Vivado и Git. Возможно, это конечный дизайн, возможно - сабмодуль для другого дизайна. Процедура добавления test bench'ей (далее TB) отличаться не будет, поэтому дальнейшее рассмотрение продолжим на примере сабмодуля imitator.

Задача - добавить TB'и для модулей imitator'а, причем

- они должны храниться в СКВ и быть доступны всем разработчикам,

- имеются в виду TB'и на языке Verilog для симуляторов типа Vivado Simulator, ModelSim и т.д., а не тесты на языках Си или Matlab для Verilator'а.

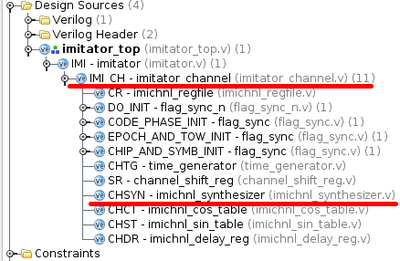

Для конкретики, будем добавлять в дизайн imitator TB'и для двух модулей:

- imichnl_synthesizer, отвечающий за фазу несущей,

- imitator_channel, являющийся топ-модулем для одного канала имитатора и включающий в себя первый модуль.

Наша задача разбивается на несколько этапов:

- написать код самих TB'ей, запустить, получить результаты,

- понять, какие файлы охватывает TB,

- внести изменения в скрипт регенерации проекта так, чтобы сохранились все настройки и файлы TB.

Приведу один из вариантов решения подзадач, не требующий знания tcl скриптов и опирающийся по-максимуму на GUI.

Написание TB'ей

Накидаем через GUI новый TB, а потом перенесем его в tcl-скрипт! Начнем с TB для модуля imichnl_synthesizer.

В Flow Navigator (это панель слева в Vivado) в разделе Simulation выбираем Simulation Settings

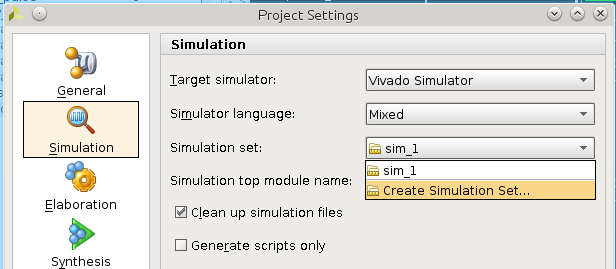

В открывшемся окне в разделе Simulation в графе Simulation top modulw name создаем новый файлсет, выбирая Create Simulation Set

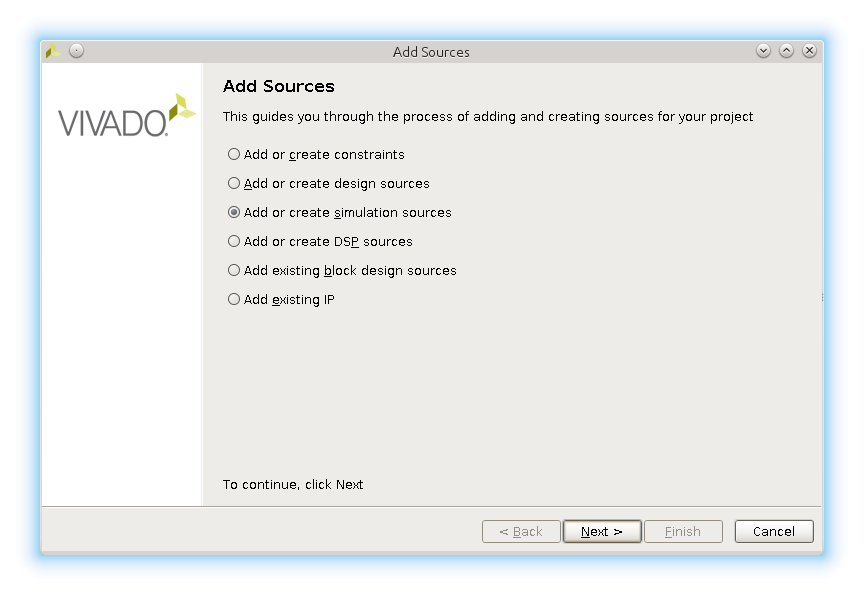

Далее Add or create simulation sources

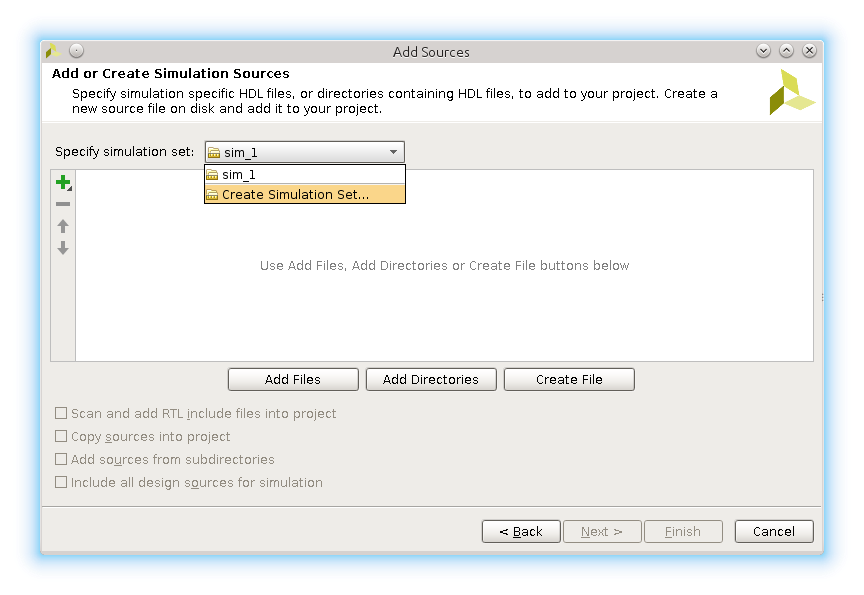

В следующем окне создаем новый fileset для симуляции через Specify simulation set -> Create Simulation Set.

ВНИМАНИЕ Не занимайте и не удаляйте файлсет sim_1. Vivado его очень любит и будет создавать заново, делая при этим активным. Лучше оставить sim_1 пустым.

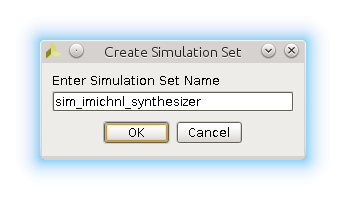

Новому файлсету даем осмысленное название, например, sim_imichnl_synthesizer

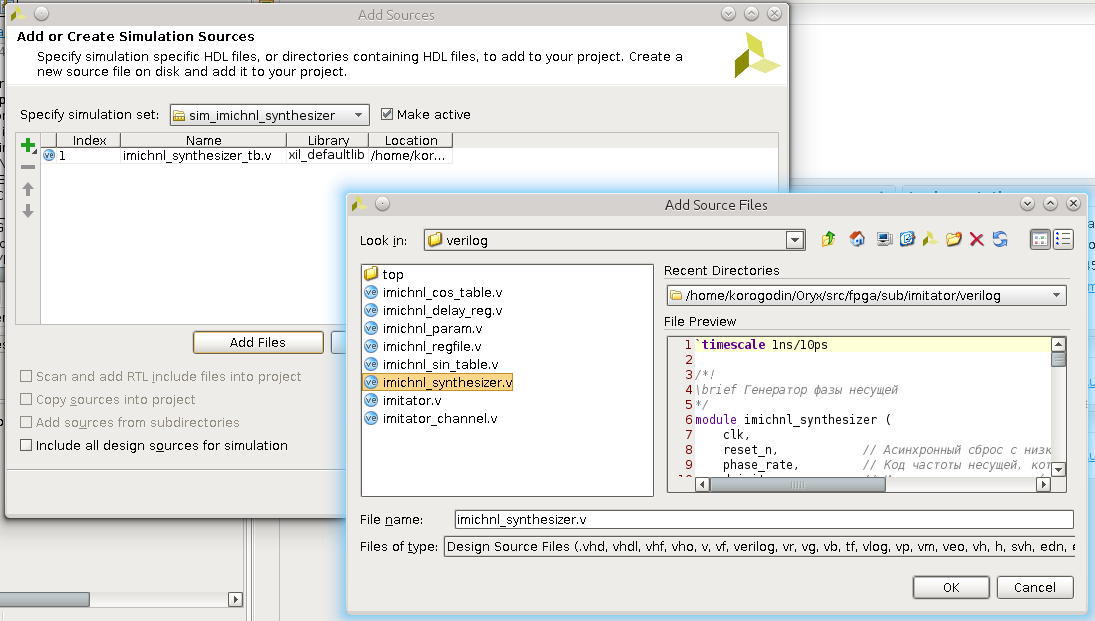

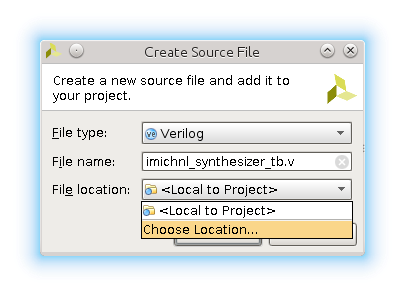

В том же окне Add Sources можем пометить новый TB как активный. Добавляем новый файл TB'а, нажимая кнопку Create File. Даем файлу осмысленное имя с суффиксом tb, например, imichnl_synthesizer_tb.v и обязательно указываем в качестве пути каталог tb дизайна imitator:

С помощью кнопки Add Files добавляем уже существующие файлы, которые потребуются для работы тестируемого модуля. В данном случае это сам модуль imichnl_synthesizer из каталога verilog