19.02.2016 Моделирование verilog

Материал из SRNS

Boldenkov (обсуждение | вклад) |

Korogodin (обсуждение | вклад) |

||

| Строка 49: | Строка 49: | ||

[[File:20160219_questa_wave_1.png|400px]] | [[File:20160219_questa_wave_1.png|400px]] | ||

| + | |||

| + | [[Categoty:FPGA]] | ||

| + | [[Categoty:ПЛИС]] | ||

| + | [[Categoty:Verilog]] | ||

| + | [[Categoty:Моделирование]] | ||

{{wl-publish: 2016-02-19 14:26:27 +0300 | Boldenkov }} | {{wl-publish: 2016-02-19 14:26:27 +0300 | Boldenkov }} | ||

Версия 22:54, 19 февраля 2016

Итак, задача состоит в том, чтобы с помощью Modelsim провести моделирование кода Verilog.

Создаём файл, который будем моделировать

`timescale 1ns/1ns

module tb();

reg clk = 1'b0;

always #5 clk=!clk;

reg [4:0] cnt=5'b0;

always @(posedge clk) begin

cnt <= cnt+1;

end

endmodule

module tb();

reg clk = 1'b0;

always #5 clk=!clk;

reg [4:0] cnt=5'b0;

always @(posedge clk) begin

cnt <= cnt+1;

end

endmodule

Первая строка задаёт темп моделирования. Строка "always #5 clk=!clk;" задаёт тактовый сигнал - каждые 5 интервалов времени, указанных в timescale. Остальной код тривиален.

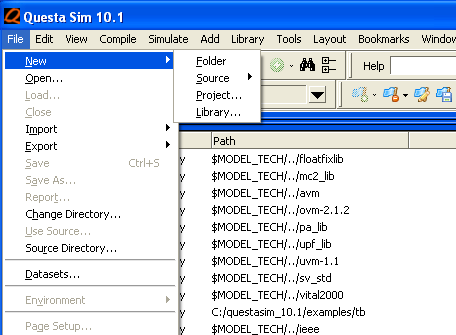

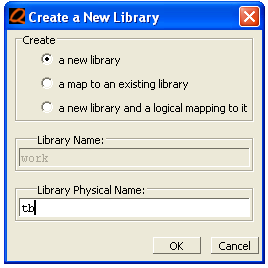

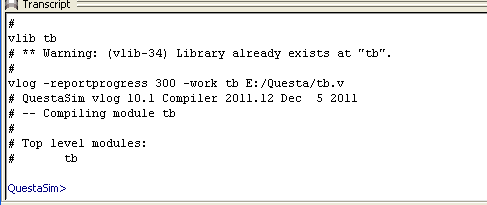

Создаём новую библиотеку. Пусть для примера она называется "tb":

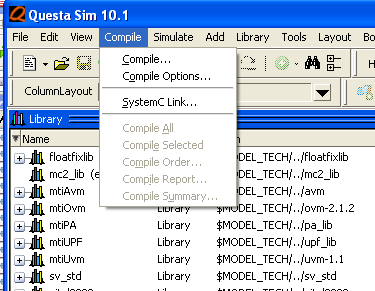

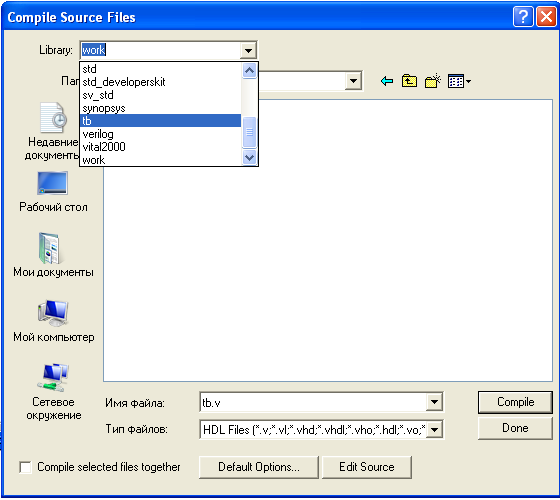

Компилируем файл verilog.

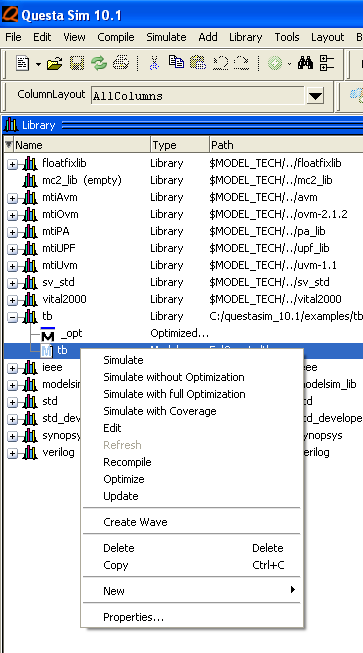

Запускаем симуляцию - без оптимизации! (Simulate without optimization)

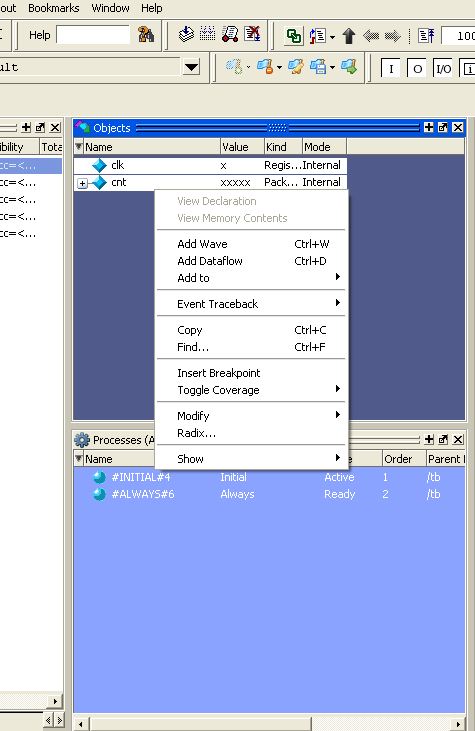

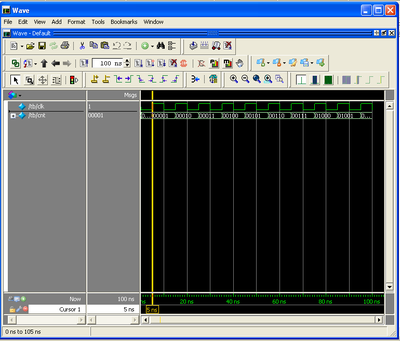

Добавляем требуемые сигналы в окно отображения Wave

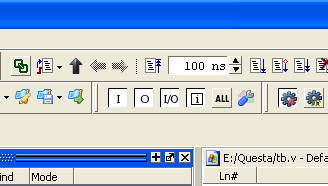

Запускаем симуляцию - выбираем длительность и нажимаем кнопку запуска (справа от поля ввода длительности)

В окне Wave смотрим результаты

Categoty:FPGA Categoty:ПЛИС Categoty:Verilog Categoty:Моделирование

[ Хронологический вид ]Комментарии

Войдите, чтобы комментировать.