19.02.2016 Моделирование verilog

Boldenkov (обсуждение | вклад) |

Boldenkov (обсуждение | вклад) (→Более сложный пример с автоматизацией процессов) |

||

| (не показаны 20 промежуточных версий 3 участников) | |||

| Строка 1: | Строка 1: | ||

<summary [ hidden ]> | <summary [ hidden ]> | ||

Всё уже забыл, решил записать. | Всё уже забыл, решил записать. | ||

| + | |||

| + | [[File:20160302_thoughts.jpg|300px|center]] | ||

</summary> | </summary> | ||

| − | |||

Итак, задача состоит в том, чтобы с помощью Modelsim провести моделирование кода Verilog. | Итак, задача состоит в том, чтобы с помощью Modelsim провести моделирование кода Verilog. | ||

| − | + | == Создаём файл, который будем моделировать == | |

<source lang="verilog"> | <source lang="verilog"> | ||

`timescale 1ns/1ns | `timescale 1ns/1ns | ||

| Строка 26: | Строка 27: | ||

Первая строка задаёт темп моделирования. Строка "always #5 clk=!clk;" задаёт тактовый сигнал - каждые 5 интервалов времени, указанных в timescale. Остальной код тривиален. | Первая строка задаёт темп моделирования. Строка "always #5 clk=!clk;" задаёт тактовый сигнал - каждые 5 интервалов времени, указанных в timescale. Остальной код тривиален. | ||

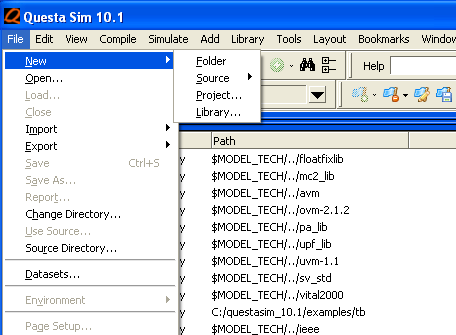

| − | + | == Создаём новую библиотеку. Пусть для примера она называется "tb": == | |

| − | [[File:20160219_questa_newlib_1.png | + | [[File:20160219_questa_newlib_1.png]] [[File:20160219_questa_newlib_2.png]] |

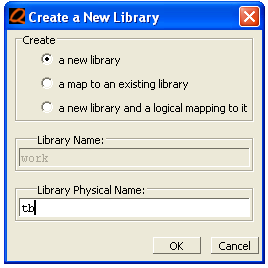

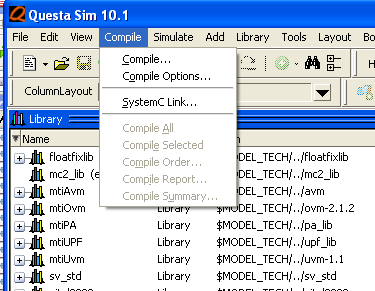

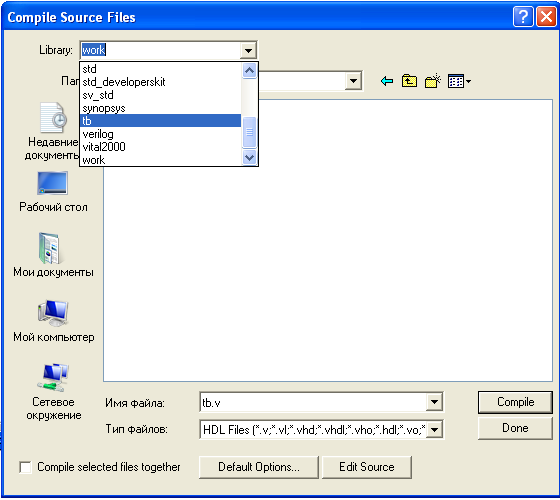

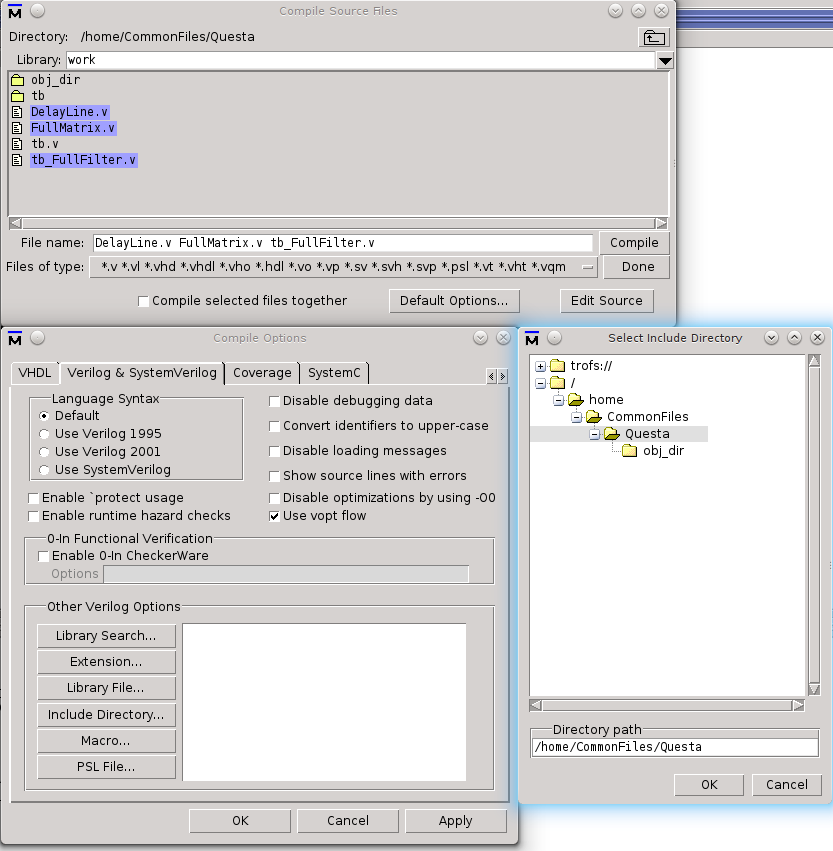

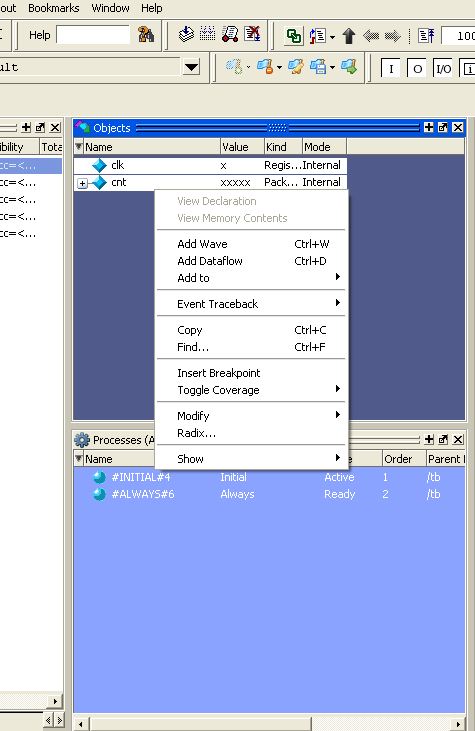

| − | + | == Компилируем файл verilog. == | |

| − | [[File:20160219_questa_compile.png | + | [[File:20160219_questa_compile.png]] [[File:20160219_questa_compile_2.png]] |

| − | + | Попутно указываем путь к подключаемым чере "`include" файлам, нажав кнопку "Default options": | |

| − | [[File: | + | [[File:20160316_MentorIncludeDIr.png]] |

| − | + | [[File:20160219_questa_compile_3.png]] | |

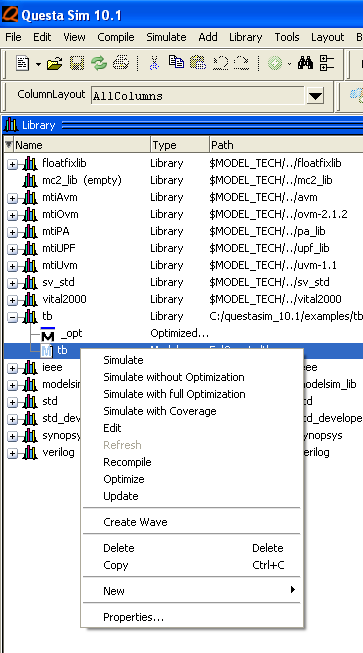

| − | + | == Запускаем симуляцию - без оптимизации! (Simulate without optimization) == | |

| − | + | [[File:20160219_questa_simulate_1.png]] | |

| − | + | == Добавляем требуемые сигналы в окно отображения Wave == | |

| − | + | [[File:20160219_questa_simulate_2.png]] | |

| + | |||

| + | == Запускаем симуляцию - выбираем длительность и нажимаем кнопку запуска (справа от поля ввода длительности) == | ||

| + | |||

| + | [[File:20160219_questa_simulate_3.png]] | ||

| + | |||

| + | == В окне Wave смотрим результаты == | ||

[[File:20160219_questa_wave_1.png|400px]] | [[File:20160219_questa_wave_1.png|400px]] | ||

| + | |||

| + | == А теперь всё то же самое - автоматически == | ||

| + | |||

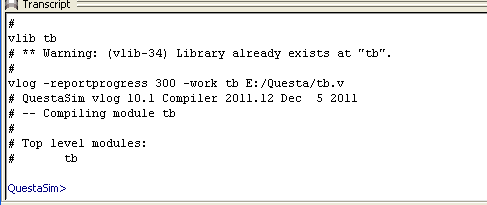

| + | Каждый раз делать всё это надоедает. Поэтому можно сделать всё из командного файла. Создаём файл "do.tcl" | ||

| + | <source lang="tcl"> | ||

| + | # vlib tb | ||

| + | vlog -reportprogress 300 -work tb /tmp/Verilog/test.v | ||

| + | vsim -novopt tb.tb | ||

| + | add wave -position instertpoint \ | ||

| + | sim:/tb/clk \ | ||

| + | sim:/tb/cnt | ||

| + | run 100ns | ||

| + | </source> | ||

| + | |||

| + | Запускаем vsim командой: | ||

| + | <source lang="bash"> | ||

| + | vsim -do do.tcl | ||

| + | </source> | ||

| + | |||

| + | В результате выдаются временные диаграммы. | ||

| + | Можно в коде тестбенча сделать запись результатов в файл, дать в конце скрипта команду exit, тогда временные диаграммы можно будет не смотреть. | ||

| + | |||

| + | == Более сложный пример с автоматизацией процессов == | ||

| + | |||

| + | Рассмотрим пример, в котором есть тестируемый модуль my_adder.v, тестбенч test.v и включаемый файл inc/params.v. | ||

| + | Будет два режима отладки: | ||

| + | * отладка с просмотром временных диаграмм в modelsim | ||

| + | * обработка данных в Matlab с помощью файла test.m | ||

| + | |||

| + | Итак, исходники: | ||

| + | * тестируемый модуль my_adder.v: | ||

| + | {{Hider|title = my_adder.v: | ||

| + | |content = <source lang="verilog"> | ||

| + | `include "params.v" | ||

| + | |||

| + | module my_adder( | ||

| + | clk, | ||

| + | resetn, | ||

| + | in, | ||

| + | sum | ||

| + | ); | ||

| + | |||

| + | parameter LENGTH=`SUM_LENGTH; | ||

| + | |||

| + | input clk; | ||

| + | input resetn; | ||

| + | input [4:0] in; | ||

| + | output [LENGTH-1:0] sum; | ||

| + | |||

| + | reg [LENGTH-1:0] sum; | ||

| + | |||

| + | |||

| + | always @(posedge clk or negedge resetn) begin | ||

| + | if (resetn == 1'b0) begin | ||

| + | sum <= 10'd0; | ||

| + | end else begin | ||

| + | sum <= sum + in; | ||

| + | end | ||

| + | end | ||

| + | endmodule // my_adder | ||

| + | </source> | ||

| + | |hidden = 1 | ||

| + | }} | ||

| + | * тесбенч test.v: | ||

| + | {{Hider|title = test.v: | ||

| + | |content = <source lang="verilog"> | ||

| + | `timescale 1ns/1ns | ||

| + | |||

| + | module tb(); | ||

| + | reg clk = 1'b0; | ||

| + | reg resetn; | ||

| + | |||

| + | initial begin | ||

| + | resetn = 0; | ||

| + | #10 | ||

| + | resetn = 1; | ||

| + | |||

| + | end | ||

| + | |||

| + | always #5 clk=!clk; | ||

| + | |||

| + | reg [4:0] cnt=5'b0; | ||

| + | |||

| + | always @(posedge clk) begin | ||

| + | cnt <= cnt+1; | ||

| + | end | ||

| + | |||

| + | wire [10:0] out; | ||

| + | |||

| + | my_adder adder | ||

| + | ( | ||

| + | .clk (clk), | ||

| + | .resetn (resetn), | ||

| + | .in (cnt), | ||

| + | .sum (out) | ||

| + | ); | ||

| + | |||

| + | integer fd_cnt; | ||

| + | integer fd_sum; | ||

| + | initial begin | ||

| + | fd_cnt = $fopen("cnt.txt", "w"); | ||

| + | fd_sum = $fopen("sum.txt", "w"); | ||

| + | end | ||

| + | |||

| + | always @(posedge clk) begin | ||

| + | if (resetn!=1'b0) begin | ||

| + | $fdisplay(fd_cnt, "%d", cnt); | ||

| + | $fdisplay(fd_sum, "%d", adder.sum); | ||

| + | end | ||

| + | end | ||

| + | |||

| + | |||

| + | endmodule // tb | ||

| + | </source> | ||

| + | |hidden = 1 | ||

| + | }} | ||

| + | * Файл параметров inc/params.v: | ||

| + | {{Hider|title = inc/params.v: | ||

| + | |content = <source lang="verilog"> | ||

| + | `define SUM_LENGTH 11 | ||

| + | </source> | ||

| + | |hidden = 1 | ||

| + | }} | ||

| + | * Тест Matlab test.m: | ||

| + | {{Hider|title = test.m: | ||

| + | |content = <source lang="matlab"> | ||

| + | clear; | ||

| + | |||

| + | system('make batch'); | ||

| + | |||

| + | fid=fopen('cnt.txt', 'r'); cnt = fscanf(fid, '%d', inf)'; fclose(fid); | ||

| + | fid=fopen('sum.txt', 'r'); sum = fscanf(fid, '%d', inf)'; fclose(fid); | ||

| + | |||

| + | plot([cnt; sum]') | ||

| + | </source> | ||

| + | |hidden = 1 | ||

| + | }} | ||

| + | |||

| + | Автоматизация процессов будет осуществляться с помощью make. | ||

| + | {{Hider|title = Makefile: | ||

| + | |content = <source lang="make"> | ||

| + | INC=inc | ||

| + | SRC=test.v my_adder.v | ||

| + | |||

| + | .PHONY: all show batch compile clean | ||

| + | |||

| + | all: show | ||

| + | |||

| + | show: compile | ||

| + | vsim -do show.tcl | ||

| + | |||

| + | batch: compile | ||

| + | vsim -c -do batch.tcl | ||

| + | |||

| + | compile: tb | ||

| + | if [ -f vlog.opt ]; then rm vlog.opt; fi | ||

| + | for i in $(INC); do \ | ||

| + | echo "+incdir+$$i" >> vlog.opt; \ | ||

| + | done | ||

| + | |||

| + | if [ -f compile.tcl ]; then rm -f compile.tcl; fi | ||

| + | for i in $(SRC); do \ | ||

| + | echo "vlog -reportprogress 300 -work tb $$i" >> compile.tcl; \ | ||

| + | done | ||

| + | |||

| + | tb: | ||

| + | if [ ! -d tb ]; then \ | ||

| + | vsim -c -do lib.tcl; \ | ||

| + | fi | ||

| + | |||

| + | clean: | ||

| + | rm -Rf *.txt transcript vsim.wlf tb vlog.opt | ||

| + | </source> | ||

| + | |hidden = 1 | ||

| + | }} | ||

| + | |||

| + | Цель all стоит в Makefile первой, она будет выполнятся при запуске make. Можно ставить в зависимость show, тогда откроется окно modelsim с временными диаграммами, либо batch, тогда modelsim выполнит моделирование в командном режиме и результаты будут записаны в файлы cnt.txt и sum.txt. | ||

| + | |||

| + | Цель compile создаёт файл compile.tcl, используемый для компиляции файлов verilog. Цель tb создаёт библиотеку tb, в которой будет происходить моделирование. Цель clean очищает каталог от всех создаваемых при работе файлов. | ||

| + | |||

| + | При выполнении make show исполняется файл show.tcl. В этом файле перечислены сигналы, которые выводятся в окно wave и даётся команда run. | ||

| + | {{Hider|title = show.tcl: | ||

| + | |content = <source lang="tcl"> | ||

| + | do compile.tcl | ||

| + | |||

| + | vsim -novopt tb.tb | ||

| + | add wave -position instertpoint \ | ||

| + | sim:/tb/clk \ | ||

| + | sim:/tb/resetn \ | ||

| + | sim:/tb/cnt \ | ||

| + | sim:/tb/out \ | ||

| + | sim:/tb/adder/sum | ||

| + | run 300ns | ||

| + | </source> | ||

| + | |hidden = 1 | ||

| + | }} | ||

| + | |||

| + | При выполнении make batch исполняется файл batch.tcl: | ||

| + | {{Hider|title = batch.tcl: | ||

| + | |content = <source lang="tcl"> | ||

| + | do compile.tcl | ||

| + | |||

| + | vsim -novopt tb.tb | ||

| + | run 300ns | ||

| + | quit -f | ||

| + | </source> | ||

| + | |hidden = 1 | ||

| + | }} | ||

| + | |||

| + | Теперь можно сразу из Matlab запускать test.m и всё будет работать. Можно вызывать make show и будут временные диаграммы в modelsim. | ||

| + | |||

| + | Ссылка на архив с файлами: [[:File:20161104_verilog_test.tar.bz2]] | ||

| + | |||

| + | [[Category:FPGA]] | ||

| + | [[Category:ПЛИС]] | ||

| + | [[Category:Verilog]] | ||

| + | [[Category:Моделирование]] | ||

{{wl-publish: 2016-02-19 14:26:27 +0300 | Boldenkov }} | {{wl-publish: 2016-02-19 14:26:27 +0300 | Boldenkov }} | ||

Текущая версия на 11:53, 4 ноября 2016

Итак, задача состоит в том, чтобы с помощью Modelsim провести моделирование кода Verilog.

[править] Создаём файл, который будем моделировать

module tb();

reg clk = 1'b0;

always #5 clk=!clk;

reg [4:0] cnt=5'b0;

always @(posedge clk) begin

cnt <= cnt+1;

end

endmodule

Первая строка задаёт темп моделирования. Строка "always #5 clk=!clk;" задаёт тактовый сигнал - каждые 5 интервалов времени, указанных в timescale. Остальной код тривиален.

[править] Создаём новую библиотеку. Пусть для примера она называется "tb":

[править] Компилируем файл verilog.

Попутно указываем путь к подключаемым чере "`include" файлам, нажав кнопку "Default options":

[править] Запускаем симуляцию - без оптимизации! (Simulate without optimization)

[править] Добавляем требуемые сигналы в окно отображения Wave

[править] Запускаем симуляцию - выбираем длительность и нажимаем кнопку запуска (справа от поля ввода длительности)

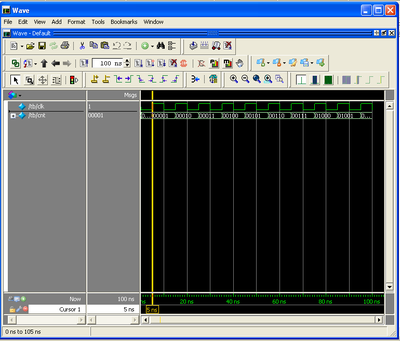

[править] В окне Wave смотрим результаты

[править] А теперь всё то же самое - автоматически

Каждый раз делать всё это надоедает. Поэтому можно сделать всё из командного файла. Создаём файл "do.tcl"

vlog -reportprogress 300 -work tb /tmp/Verilog/test.v

vsim -novopt tb.tb

add wave -position instertpoint \

sim:/tb/clk \

sim:/tb/cnt

run 100ns

Запускаем vsim командой:

В результате выдаются временные диаграммы. Можно в коде тестбенча сделать запись результатов в файл, дать в конце скрипта команду exit, тогда временные диаграммы можно будет не смотреть.

[править] Более сложный пример с автоматизацией процессов

Рассмотрим пример, в котором есть тестируемый модуль my_adder.v, тестбенч test.v и включаемый файл inc/params.v. Будет два режима отладки:

- отладка с просмотром временных диаграмм в modelsim

- обработка данных в Matlab с помощью файла test.m

Итак, исходники:

- тестируемый модуль my_adder.v:

module my_adder(

clk,

resetn,

in,

sum

);

parameter LENGTH=`SUM_LENGTH;

input clk;

input resetn;

input [4:0] in;

output [LENGTH-1:0] sum;

reg [LENGTH-1:0] sum;

always @(posedge clk or negedge resetn) begin

if (resetn == 1'b0) begin

sum <= 10'd0;

end else begin

sum <= sum + in;

end

end

endmodule // my_adder

- тесбенч test.v:

module tb();

reg clk = 1'b0;

reg resetn;

initial begin

resetn = 0;

#10

resetn = 1;

end

always #5 clk=!clk;

reg [4:0] cnt=5'b0;

always @(posedge clk) begin

cnt <= cnt+1;

end

wire [10:0] out;

my_adder adder

(

.clk (clk),

.resetn (resetn),

.in (cnt),

.sum (out)

);

integer fd_cnt;

integer fd_sum;

initial begin

fd_cnt = $fopen("cnt.txt", "w");

fd_sum = $fopen("sum.txt", "w");

end

always @(posedge clk) begin

if (resetn!=1'b0) begin

$fdisplay(fd_cnt, "%d", cnt);

$fdisplay(fd_sum, "%d", adder.sum);

end

end

endmodule // tb

- Файл параметров inc/params.v:

- Тест Matlab test.m:

system('make batch');

fid=fopen('cnt.txt', 'r'); cnt = fscanf(fid, '%d', inf)'; fclose(fid);

fid=fopen('sum.txt', 'r'); sum = fscanf(fid, '%d', inf)'; fclose(fid);

plot([cnt; sum]')

Автоматизация процессов будет осуществляться с помощью make.

SRC=test.v my_adder.v

.PHONY: all show batch compile clean

all: show

show: compile

vsim -do show.tcl

batch: compile

vsim -c -do batch.tcl

compile: tb

if [ -f vlog.opt ]; then rm vlog.opt; fi

for i in $(INC); do \

echo "+incdir+$$i" >> vlog.opt; \

done

if [ -f compile.tcl ]; then rm -f compile.tcl; fi

for i in $(SRC); do \

echo "vlog -reportprogress 300 -work tb $$i" >> compile.tcl; \

done

tb:

if [ ! -d tb ]; then \

vsim -c -do lib.tcl; \

fi

clean:

rm -Rf *.txt transcript vsim.wlf tb vlog.opt

Цель all стоит в Makefile первой, она будет выполнятся при запуске make. Можно ставить в зависимость show, тогда откроется окно modelsim с временными диаграммами, либо batch, тогда modelsim выполнит моделирование в командном режиме и результаты будут записаны в файлы cnt.txt и sum.txt.

Цель compile создаёт файл compile.tcl, используемый для компиляции файлов verilog. Цель tb создаёт библиотеку tb, в которой будет происходить моделирование. Цель clean очищает каталог от всех создаваемых при работе файлов.

При выполнении make show исполняется файл show.tcl. В этом файле перечислены сигналы, которые выводятся в окно wave и даётся команда run.

vsim -novopt tb.tb

add wave -position instertpoint \

sim:/tb/clk \

sim:/tb/resetn \

sim:/tb/cnt \

sim:/tb/out \

sim:/tb/adder/sum

run 300ns

При выполнении make batch исполняется файл batch.tcl:

vsim -novopt tb.tb

run 300ns

quit -f

Теперь можно сразу из Matlab запускать test.m и всё будет работать. Можно вызывать make show и будут временные диаграммы в modelsim.

Ссылка на архив с файлами: File:20161104_verilog_test.tar.bz2

[ Хронологический вид ]Комментарии

Войдите, чтобы комментировать.